Sure, the uber-trendy wearable Internet of Things (IoT) markets look promising. But the enticing baubles on the outside mask some real stumbling blocks when it comes to chasing the elusive sweet spot of increased mobility, performance and more features.

In the case of wearables, increased portability equates to size and weight reductions. For IoT more generally delivering extended lifetimes that enable “fit and forget” capability needs a level of hitherto unparalleled energy conservation. This means product viability in many cases.

The short-term demand for both increased battery life and reduced product size can only be realised, it seems, by reducing the circuit power consumption. And the secret may well be near-threshold low voltage design.

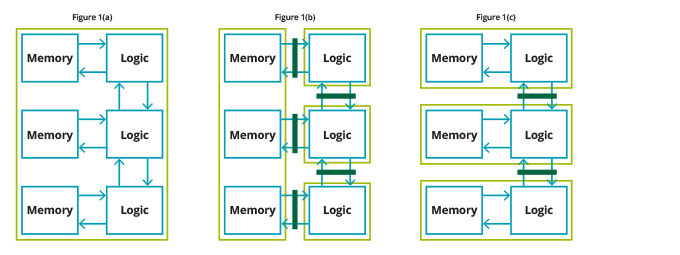

The relationship between frequency, voltage, and power has become an important factor in the SoC design when subsystems that have low throughput requirements run at low frequency and low voltage. Techniques such as Dynamic Voltage and Frequency Scaling (DVFS) are now mainstream.

Figure 1(a) shows the traditional single power domain approach, while figures 1(b) and 1(c) show alternatives with multiple power domains.

The ultimate aim is for each subsystem to run no faster than necessary at a voltage no higher than required to enable that operating speed. Fortunately, many wearable and IoT sensor applications, with their low performance requirements are amenable to this design approach.

Near Threshold SRAM Design

Circuit design using operating voltages that are much closer to the transistor threshold voltage successfully address the demand for lower operating power. However, there is a problem; Traditional SRAM designs won’t allow such scaling due to bit cell operating voltage restrictions.

sureCore has arrived at a more practical approach. Our low power SRAM IP combines standard foundry bit cells with a suite of patented power saving circuit techniques to deliver low-power, area efficient memories that require no process changes.

sureCore EverOn™ SRAM operates across a much wider operating voltages range than traditional SRAM using the same foundry bit cell. Novel circuit designs, architectural techniques, and assist circuits create SRAM IP that operates with supply voltages between 1.21V and 0.6V on a commercially-available 40ULP node, across process corners, with a -40°C to +125°C temperature range.

Operating with a very low supply voltage eliminates the need for a separate higher-voltage SRAM supply and removes the need for level-shifting buffers between logic and memory. Similarly, the wide operating voltage range means that the memory is suitable for designs using DVFS across a very wide frequency range, from a few to several hundred MHz.

Internally, the memories have a bank-based architecture that support completely independent per-bank active, sleep, and shutdown modes to allow leakage power to be tuned based on the activity pattern. There is no need for separate low-voltage and high-speed memories. EverOnTM memories meet both requirements.

IoT and wearable growth will only be possible with energy conservation changes and extended battery life that is measured in months and years rather than hours and days. The key will be much improved power management capabilities and the spreading popularity of Near Threshold design. Until now this was hindered by the lack of efficient memory solutions. By delivering a true near threshold SRAM equipped with power management features optimised for system level architectural trade-offs sureCore has transformed the design landscape.